## DIFFERENTIAL NON-LINEARITY CORRECTION FOR SUCCESSIVE APPROXIMATION ADC

Associ. Prof. Dr. Hikaru YAMADA

Department of Electronics Faculty of Engineering Hiroshima-Denki Inst. of Tech., Hiroshima, JAPAN

Abstract: In this paper a new method to correct the differential non-linearity(D NL) error for a successive approximation is proposed. The DNL of ADC is very important characteristic in the field of radiation pulse height analysis or measurement of probability density function. The results of computer simulations are shown to demonstrate the feasibility of the proposed correction method.

#### 1. Introduction

The ADC which is used in a multichannel pulse height analyzer(PHA) or a measureing instrument of probability density function must have excellent differential linearity. Because of its good differential linearity and simple circuit, the Wilkinson type is still extensively used as an ADC for pulse height analyzers, but it has comparatively long conversion time. The successive approximation type ADC has quite short conversion time and is easy to get, but has very wrong differential linearity. The "Sliding Scale Method" by Gatti was introduced about 25 years ago to compensate the channel width inaccuracies of successive approximation ADC. The aim of this paper is to propose a new method to correct the DNL error of amplitude distribution curve which is measured by successive approximation ADC.

# DNL analysis of successive approximation ADC

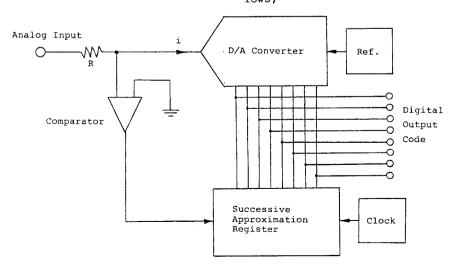

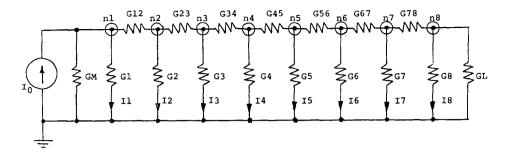

Block diagram of successive approximation ADC is shown in Fig.l. It is clear that the largest cause for the DNL error of successive approximation ADC is the differential linearity of D/A converter (DAC) in it. The basic ADC circuit (ladder resistor network) is shown in Fig.2. where, I $_0$ :Constant current, G:Conductance, I $_1$ -I $_8$ : $^{2n}$  weighted current, n:nodes for circuit analysis. For the ladder resistor network in Fig.2, we can get the circuit equation in the form of a matrix equation (1). Where,  $i_1$ -i $_8$  are the current flowing into the nodes  $n_1$ -n $_8$  respectively. and  $v_1$ -v $_8$  are node voltages respectively.  $i_1$ =I $_0$ ,  $i_2$ = $i_3$ =...= $i_8$ =0

Solving the equation (1) with respect to  $v_1$ - $v_8$ , we get the output current of DAC.

Since the registors which are used in the DAC are not ideal, the output current of DAC is not olso ideal. Moreover, it is impossible to obtain the ideal semiconductor switch.

The differential linearity error of DAC is the amount of deviation of any quantum from its ideal value. In other words, it is the deviation in the analog difference between two adjacent codes from the ideal value of Full scale range/2<sup>n</sup>.

The output current is explained as follows,

Fig.1 Block diagram of successive approximation ADC.

Fig.2 Ladder resistor network.

$$I_{out} = s_1^{G_1}v_1^{+}s_2^{G_2}v_2^{+}\cdots + s_8^{G_8}v_8$$

=  $s_1^{I_1}+s_2^{I_2}+\cdots + s_8^{I_8}$  (2)

Where,  $s_1-s_8$  are the DAC input code 0 or 1.

The channel width  $\Delta v_k$  are proportional to the output current  $^k\mathrm{difference}$  of DAC.

$$\Delta V_k \propto (I_{\text{out},k+1}^{-1}I_{\text{out},k})$$

(3)

The differential non-linearity error  $_{\mbox{\footnotesize DNL}}$  is defined as

$$\mathcal{E}_{DNL} \stackrel{\Delta}{=} \frac{\max \cdot [\det \cdot (\Delta V_k - \overline{\Delta V})]}{\overline{\Delta V}} \times 100 [\$]$$

Where, max.[·] gives maximum value  $\frac{\text{det.}(\cdot)}{\Delta V}$  is average of  $\Delta V_k$

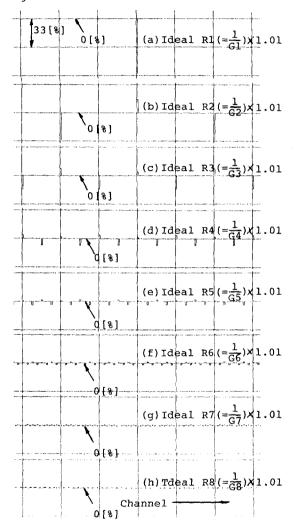

Fig. 3 shows the channel width excursions from the ideal when one of resistor deviates 1[%] from the ideal. The MSB registor generates the biggest DNL. The LSB registor generates small but many DNL.

## Establishment of algorithm for DNL error correction

$$\overline{\Delta V} \times \frac{\alpha}{100} \times S = \overline{\Delta V} \times \frac{\beta}{100} \times (N-S)$$

(5)

This reduces to,

More over, we obtain,

$$\sum_{i=1}^{S} \frac{C_{s,i}}{1+\frac{\alpha}{100}} + \sum_{j=1}^{N-S} \frac{C_{r,j}}{1-\frac{\beta}{100}} = \sum_{i=1}^{S} C_{s,i} + \sum_{j=1}^{N-S} C_{r,j}$$

Where,  $C_{s,i}$  (i=1,2,...,S) are the counting data of increased channel width.  $C_{r,j}$  (j=1,2,...,N-S) are the counting data of decreased channel width. That is to say, the sum of compensated counting number is equal to the total non-compensated counting number.

Fig.3 Excursions of  $V_k$  from the ideal when just one resistor deviates independently from the ideal.

We now solve equation (6) and (7) for the correction coefficients X and S. We thus obtain,

$$A = \left[X \cdot \frac{N-S}{S} - Y\right] / (X+Y)$$

(8)

$$B = [X - Y \cdot \frac{S}{N-S}] / (X+Y)$$

(9)

Where,

$$A \stackrel{\Delta}{=} \frac{\alpha}{100}$$

(10)

$$B \stackrel{\Delta}{=} \frac{\cancel{\beta}}{100} \tag{11}$$

$$X \stackrel{\Delta}{=} \sum_{i=1}^{S} C_{s,i}$$

(12)

$$Y \stackrel{\Delta}{=} \sum_{j=1}^{N-S} c_{r,j}$$

(13)

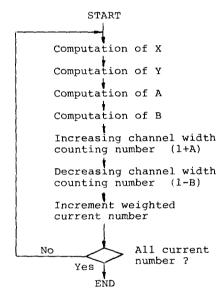

Employing the solusion A and B, we can establish the following algorithm in the form of a flowchart in fig.4.

Fig.4 Flowchart for the proposed DNL error correction algorithm.

First, we compute the sum X and Y. And next, we compute A and B using X and Y. Then we multiply (1+A) to all channels of which the channel width is increased. And next, we multiply (1-B) to all channels of which the channel width is decreased. We repeat this procedure for all weighted current number. If necessary, whole procedure is repeated.

#### 4. Computer simulations

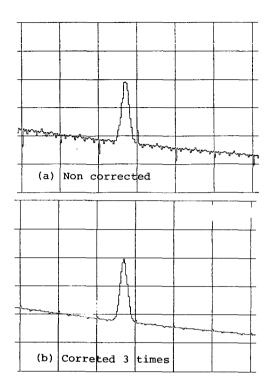

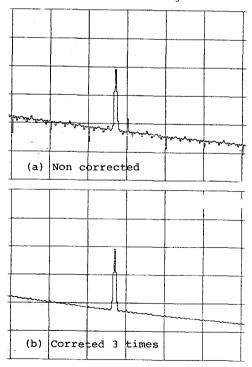

On the assumption that a Gaussian distributed random pulses are exist in the background pulses, the computer simulations are carried out. A personal computer and the BASIC language are used. The results are shown in Fig.7 and Fig. 8. As we can see in Fig.8, very small standard deviation is used for the signal. Nevertheless, the DNL error is well corrected. It is evident that if we use some smoothing technique to reduce the DNL error, for example "the mooving average", the signal will surely destroyed.

Fig.7 Computer simulation for a Gaussian random signal.

Fig.8 Computer simulation for a Gaussian signal with small standard diviation.

## 5. Conclusions

A new algorithm to correct the DNL of the successive approximation ADC is proposed in this paper. The remarkable feature of this method is that the effect of DNL error correction is independent of temperature. This method does not disturb the fastness and the dynamic range of the successive approximation ADC.

## 6. Acknowledgement

The author would like to express the cordial thanks to Dr. T.Munakata of Hiroshima-Denki Institute of Technology for his constant guidance.

### References

- [1] D.H.Wilkinson : Proc. Cambridge Phil. Soc., Vol.46,508(1949)

- [2] P.W.Nicholson : Nuclear Electronics, WILEY, 303/336(1974)

- [3] C.Cottini, E.Gatti, & V.Svelto : A Sliding Scale Analog To Digital Converter for Pulse Analysis, Proc. of ISNE Paris (1963)

- [4] E.Gatti, P.F.Manfredi, D.Marino: analysis and Characterization of cyclic-Scale Compensated Analog-To-Digital Converters, Nuclear Instruments and Methods, 225/230, 165 (1979)