# Floating poly-Si 상에 형성되는 자연 산화막 제어를 통한 C&M 제품의 Programming 특성 향상에 관한 연구

# Investigation of controlled native oxidation in surface of Floating poly-Si at C&M products

\*김인식 <sup>1</sup>, <sup>#</sup>이공수 <sup>2</sup>, 성훈제 <sup>3</sup>, 소친호 <sup>3</sup>, 이상우 <sup>3,</sup> 최수옥 <sup>3</sup>, 상재호 <sup>3</sup> \*I. S. Kim<sup>1</sup>, <sup>#</sup>K. S. Lee(alfredo.lee@samsung.com)<sup>2</sup>, H. J. Sung<sup>3</sup>, J. H. So<sup>3</sup>, S. W. Lee<sup>3</sup>, S. G. Choi<sup>3</sup>, J. H. Sang<sup>3</sup> 삼성전자공과대학교 반도체공학과, <sup>2</sup>삼성전자공과대학교, <sup>3</sup>삼성전자

Key words: LPCVD, Native Oxide

#### 1. 서론

Device 의 Shrink 에 따른 Cell size 의 감소는 C&M 제품소자의 요구특성 확보에 있어서 여러 가지 문제점들을 야기하고 있다. LPCVD 방식으로 증착된 Poly-Si 박막은 표면의 Roughness 가 우수하며, Dopant 나 불순물들의 Penetration length 가 짧아서 배선용 매질로 많이 이용되어 연구의 목적은 Floating poly-Si(F-poly)층의 Patterning 을 위한 Hard mask 재료인 Low Pressure Chemical Vapor Deposition (LPCVD) 방식의 SiN 박막 증착 시 F-poly / SiN 계면에 발생하는 자연 산화막 형성이 소자의 Programming 특성에 많은 영향을 미치는 것에 대하여 연구하였다. 이에 우리는 자연 산화막에 의한 소자의 특성 변화에 대해 F-poly/SiN 사이 계면에 Native Oxide 형성으로 인한 소자의 Programming 특성 불량이 유발하는 것으로 Modeling 하여 집중적인 분석을 하였다.

# 2. 본론

#### 2-1 현상 분석

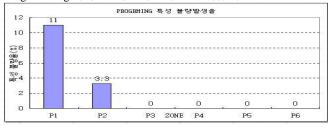

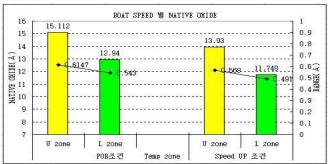

Fig.1.에서 보여주듯 Programming 특성의 불량 상관 관계를 분석하였고 그 결과는 동일 Batch type 반응로의 P1 zone,P2 zone 에서만 특성 불량이 발생했으며, 설비 구조상 P1 zone,P2 zone 은 Native Oxide 에 취약 하다는 것을 확인할 수 있었다. 이러한 Modeling은 절연막의 Bird's beak 에 의한 문제로 판단되었고, 이는 Native Oxide 가 주요 인자임이 확인되었다. 위 Process 에서 Native Oxide 의 형성 과정은 F-poly 박막 증착 후, Si wafer 가 SiN 박막 증착을 위해 반응로(Furnace tube) 안으로 Loading 될 때 F-poly 박막의 Si(silicon)원자와 반응로 내의 O2 원자가 Si-Wafer 표면에서 반응되어 산화되는 것이 직접적인 원인이 되는 것으로 Modeling 하고, Batch type 인 LPCVD 설비의 Standby 온도, Loading speed, Pumping rate 가 가장 중요한 핵심인자라는 관점으로 공정 Parameter 들에 대한 실험을 진행을 하여 균일한 산화막 제어를 통해 제품의 Programming 특성을 개선하고자 연구하였다.

Fig.1. Furnace Tube zone Programming Attribute failure rate

Fig.2 와 같이 특성 불량 발생 부위를 SEM 으로 확인 하였을 때, Bridge point 를 확인하였다

Fig.2. Pattern bridge SEM Picture of Bird's beak

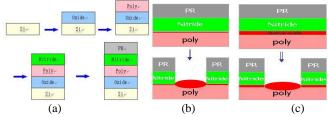

Fig.3(a)는 본 실험에서의 Process Sequence 를 보여준다 (b)Normal Inter poly oxide(IPO)의 성장과정이지만 (c)는 Poly 막질 위 계면에 Native Oxide 가 이상 Growing 된 뒤 IPO 가 Abnormal 성장된 과정을 보여 준다.

Fig.3. (a) Process Sequence (b)Normal Sequence (c)Abnormal Sequence

### 2-2 실험

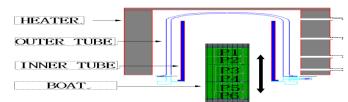

Fig.4.의 설비의 구조를 Vertical LPCVD 장비의 반응로의 Flow mechanism 을 알 수 있는데 O2 와 N2 가 Inner tube → Outer tube → 배기 순으로 배출된다. 주요 인자인 O2 는 Process wafer charge 된 Boat 가 반응로에 Loading 될 때, 내부로 많이 유입되면서 반응로의 높은 온도와 함께 SiN 박막 전 Poly-si 막질 위에 Native-Oxide 를 growing 하는 것을 알 수 있었다.

Fig.4. A schematic diagram of the furnace

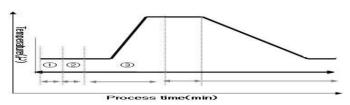

Fig.4. 의 구조적인 취약 Point 와 Fig5 의 Heat cycle chart 를 참고하여 Native-Oxide Growing 이 가능한 인자를 세분화하여 주요 인자로 Modeling 하고 세 가지 종류의 실험을 진행하였다. 참고로 Native-Oxide 의 두께측정 장비로는 K5X(KLA TENCOR)를 사용 하였다..

| Step No | Step 명        | Factor       |  |

|---------|---------------|--------------|--|

| 1       | Load          | Speed        |  |

| 2       | Stand by temp | Temp         |  |

| 3       | Slow pumping  | Pumping rate |  |

Fig.5. Heat cycle chart and Process conditions with Various

. 첫 번째 실험으로 Boat speed 를 Table.1. 의 조건으로 변경하여 진행하였다. 설비구조상 Top 부위가 반응로 내부에서 볼 때 가장 많은 노출이 되어 취약하다는 판단에서 Speed up 을 하며 P-type si wafer 에 N2 20[l], Temperature 를 Normal process 조건으로 하여, Boat speed 에 따른 Thickness of oxide(TOX) data 변화를 측정 하였을 때 Fig.6 에서 보듯이 조건에 따라 최대 1 Å 변화를 확인 할 수 있었다.

Fig.6. Native Oxide thickness with Various Boat speeds

두 번째 실험으로 반응로 내부의 Gas 의 Residence Time을 줄이기 위하여 Pumping rate 을 변경하여 실험을 진행하였다. Boat loading 된 후 Pumping 을 하는데, Table2 와 같이 기존보다 빠른 Pumping rate 으로 반응로 내 O2 를 빨리 제거하기 위하여 Orifice 의 내경을 크게 하여 평가 진행하였다. 이에 대한 평가는 실제 Wafer 에 적용하여 확인하였다.

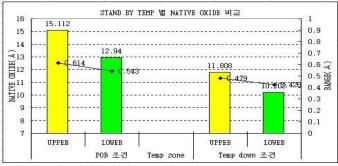

세 번째 실험의 결과로 Native Oxide 확인 시 기존대비 온도를 15% 하향한 조건에서 Native Oxide 의 두께가 기존조건보다 약 3 Å 가량 낮게 나오는 것을 Fig.7 와 같이 확인하였다. Standby 온도 하향 조건이 Native Oxide 의 성장을 억제하는데 탁월한 효과를 가짐을 알 수 있었다.

Fig.7. Native Oxide thickness with various standby temperatures

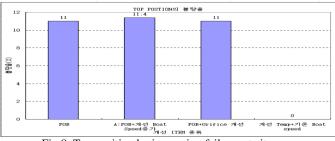

세 가지 실험을 통하여 Boat speed 와 Orifice 를 변경하였을 때는 별다른 결과가 없었지만 Top position 불량율(Fig.8)과 실험 Item 별 수율(Table.4)결과와 같이 Stand by 온도를 내렸을 때 Bird's beak 에 의한 Bridge 현상이 예방되어 가장 효과적임이 확인 되었고, 이는 Standby 온도 Control 로 Native Oxide 막의 두께를 감소시키는 것이 가장효과적임을 보여주는 것으로써, 본 연구에서 논의된 Programming 불량이 F-poly Si 과 SiN 사이에서의 Native Oxide 형성에 의한 것임을 확인할 수 있었다.

Fig.8. Top position by improving failure rate item

| 구분  | 실험 조건   |

|-----|---------|

| 1st | POR 조건  |

| 2nd | 200% 증가 |

Table.1. Process conditions with various boat speeds

| 구분  | 실험 조건      |  |

|-----|------------|--|

| 1st | POR 조건     |  |

| 2nd | 140% 증가 조건 |  |

Table.2. Process conditions with various pumping rates

| 구분  | 실험 조건                                             |  |

|-----|---------------------------------------------------|--|

| 1st | POR 조건                                            |  |

| 2nd | temp:기존대비 15% down + N2:20ℓ +<br>boat speed:기존 조건 |  |

Table.3. Process conditions with standby temperatures

| 항목            | 세부 조건                                   | 수율 |

|---------------|-----------------------------------------|----|

| Boat<br>Speed | 기존 Temp + 기존 Boat Speed                 | 동  |

|               | 기존 Temp + 개선 Boat Speed<br>(100%증가)     | 동등 |

| Orifice       | 기존 Temp + Speed + Orifice<br>내경(140%증가) | 동등 |

| Temp          | 기존 Temp + 기존 Boat Speed                 | 동등 |

|               | 개선 Temp(15% temp) + 기존 Boat Speed       | 우수 |

Table.4. Wafer-level yields of various process conditions

## 3. 결 론

C&M 제품의 Programming 특성불량은 Cell을 형성 하는 구간인 F-poly Photo mis-align, SiN / F-poly 박막, IPO, F-poly etch 등과 연관이 있는 것으로 알려져 있다. 본 논문에서는 F-poly의 Mask 층인 SiN 박막 증착 시 Process 진행 설비의 구조적인 문제로 최상층 Zone 이 Temp에 가장 취약 하여 F-poly 계면 위에 Growing 된 Native Oxide 가 주요 요인이 되어 발생한 CD Bridge가 해당 불량에 어떠한 영향을 미치는지 고찰하였다. Native Oxide의 형성을 억제 하기 위하여 다양한 공정변수들의 영향성을 관찰하였으며, 그들 중 Standby 온도의 최적화를 통하여 Native Oxide 형성 억제 및 Program 불량을 효과 적으로 개선시킬 수 있었다.

#### 참고문헌

- 1. G.Depinto and J.wilson, "Optimization of LPCVD silicon Nitride Deposion Process By Use of Designed Experiments." Proceedings from the 1990 IEEE/SEMI Advanced Semiconductor Manufacturing Conference ,pp 47-53, 19902.

- 2.J.sheih," Reduction of water Contamination in a Vacuum Load Lock During Pumping form Atmosphere." SRC Technical Report No. T90125. pp 87-89, 19903

- 3. M. Y. Hao and J. C. Lee, "Electrical characteristics of oxynitrides grown on textured single-crystal silicon," Appl. Phys. Lett., vol. 60, pp.445-447, 1992.4.

- 4.J.M.C.Stork, E.Ganin, J.D.Cressler, G.L.Patton, G.A.Sai-Halasz, "Electrical and micro structural investigation of poly siliconemitter contacts for high performance bipolar VLSI", IBMJ. Res. Develop., vol31, no.6, pp.617, 1987