# Micromachined Low-Loss Low-Dispersion Elevated CPW for High-Speed Interconnects

S.-H. Jeong<sup>1</sup> · S.-N. Lee<sup>2</sup> · S.-G. Lee<sup>4</sup> · J.-G. Yook<sup>2</sup> · Y.-J. Kim<sup>3</sup> · H.-K. Park<sup>2</sup>

#### Abstract

In this paper,  $10\,\mu$  m-elevated MEMS CPWs on various substrates are presented. Effective dielectric constants of elevated CPW(ECPW) on polyimide-loaded silicon or alumina substrate are examined and characteristic impedances are also computed versus elevation height. Dispersive property of ECPW and its electromagnetic field distributions are studied through 3-D FDTD algorithm for optimum design. Attenuation of ECPW is measured with TRL calibration procedure and revealed about 3.2 dB lower than that of conventional CPW on the same low-resistivity silicon at 40 GHz. ECPW on polyimide-loaded silicon with overlapped configuration reveals 0.2 dB/mm. Especially, alumina substrate imposes better attenuation than silicon.

Key words: Elevated CPW, Low Loss, Low Dispersive, High-Speed Transmission Line

#### I. Introduction

As the clock frequency in high-speed digital circuits and computers reaches a few giga-hertz regime, low-loss and low-dispersion signal transmission line is necessary. However, the performance of conventional transmission lines such as CPW or microstrip line implemented in CMOS compatible processing is limited to support high clock frequency signal and thereby exhibits quite dispersive and lossy characteristics. Various ways have been reported to improve the characteristics of conventional transmission lines. The method of removing the silicon substrate in the vicinity of the metal could lead to fabrication issues on mess production<sup>[1],[2]</sup>. Transmission lines with polyimide layer are presented by showing measured results<sup>[3] -[6]</sup>. High-resistivity silicon (HRS) revealed low RF signal leakage similar to GaAs substrate<sup>[7]</sup>, however, HRS wafer is not cost- effective and further requires modification of standard CMOS process.

Recently, an elevated CPW geometry has been suggested without any measured data<sup>[8]</sup>. In this paper, various simulation results such as characteristic impedance, effective dielectric constant, electromagnetic field distributions, dispersive property, and signal velocity are uncovered with aid of a three dimensional finite-difference-time-domain method (3D-FDTD). Furthermore, measured total losses for transmission lines on three different substrates are presented for the performance comparison between conventional CPW and ECPW. In every case ECPWs reveal lower total loss than conventional CPW, and

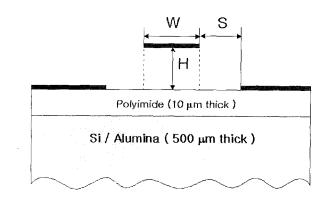

Fig. 1. Schematic of elevated coplanar waveguide on low-resistivity silicon or alumina substrate with  $10 \,\mu$ m polyimide.

overlapped ECPW shows significant improvement of dispersion characteristics, signal velocity<sup>[9]</sup>, as well as total loss in the range up to 40 GHz.

## II. Design and Fabrication

Conventional CPW supports quasi-TEM mode and is highly dispersive on CMOS grade silicon substrate due to air-dielectric interface and low resistivity, presenting limitations for the use on high-speed digital circuits. In this paper, the center signal line is  $10 \,\mu$ m-elevated in the air to minimize the dispersive

Manuscript received March 14, 2002; revised August 16, 2002.

Samsung Electronics Co. Ltd. Suwon, Korea.

<sup>&</sup>lt;sup>2</sup>Department of Electrical and Electronics Eng., Yonsei University, Seoul, Korea.

Department of Mechatronics Eng., Yonsei University, Seoul, Korea.

<sup>&</sup>lt;sup>4</sup>Samsung Advanced Institute of Technology, Yongin, Korea.

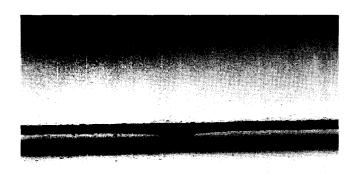

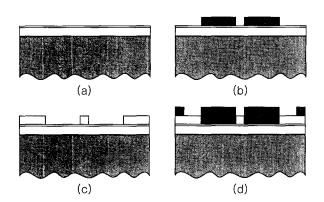

property as shown in Fig. 1. Important parameters to characte rize the ECPW performance are height of the elevated signal line(H), width(W), spacing(S) between the signal line and side ground planes, where negative value of S means the overlapped configuration. The ECPW lines having center conductor widths of  $100 \,\mu$  m and  $50 \,\mu$  m with  $10 \,\mu$  m height are fabricated as shown in Fig. 2, where the area of supporters is  $20 \times 20 \, \mu \, \text{m}^2$ . Note that the height can be  $40 \,\mu$ m to  $60 \,\mu$ m without sacrificing mechanical stability. Since the distance between the supporters is  $500 \,\mu$  m, the effect of the supporters can be neglected. Fabrication is relatively straightforward using standard liftoff processing and is compatible with standard CMOS process. In Fig. 3 fabrication procedure is described in detail. Polyimide with  $10 \,\mu$ m thickness is coated on substrate materials. The three different substrate configurations such as a CMOS grade lowresistivity silicon, a polyimide-loaded standard silicon, and a polyimide-loaded alumina, are used. Conventional CPWs(i.e.  $H=0 \mu \text{ m}$ ) with spacings  $20 \mu \text{ m}$ ,  $60 \mu \text{ m}$ ,  $100 \mu \text{ m}$  are fabricated on each case. The  $10 \,\mu$  m-ECPWs with spacing of  $-20 \,\mu$  m, 0 $\mu$  m, 20  $\mu$  m, 60  $\mu$  m, to 100  $\mu$  m, are fabricated on three different substrate configurations.

Fig. 2. SEM photograph of 10  $\mu$ m-elevated coplanar waveguide.

Fig. 3. Fabrication procedure.

- (a) polyimide and first seed-layer coating

- (b) PR coating and photo-lithography

- (c) copper plating

- (d) PR coating and photo-lithography

- (e) copper plating

- (f) second seed-layer coating

- (g) PR coating and photo-lithography

- (h) copper plating

- (i) first and second seed-layer etching

Fig. 4. Effective dielectric constant for polyimide-loaded silicon ( $\varepsilon_r = 11.9$ ) or alumina ( $\varepsilon_r = 9.5$ ).

### ∏. Theoretical Analysis

Yee's algorithm-based 3D-FDTD is used to analyze the cha-

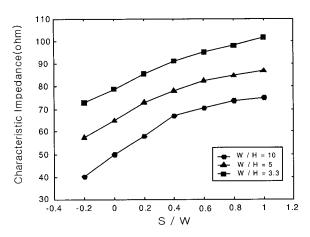

Fig. 5. Characteristic impedance for various geometry of ployimide-loaded silicon.

racteristics of the designed ECPW. Metal thickness is not considered in simulation. When signal line is elevated in the air, effective dielectric constant can be interpreted as the dielectric constant of a homogeneous medium that replaces the air and below multi-layer dielectric regions. For highly elevated geometry, very low effective dielectric constant close to 1 could be obtained for both silicon and alumina cases as shown in Fig. 4. Since signal velocity is inversely proportional to the square root of  $\varepsilon_{\it eff}$  high speed characteristic can be achieved by elevating center strip. ECPWs with negative S reveal minimum substrate dependency. As S increases  $\varepsilon_{\it eff}$  for alumina is much less than that of Si.

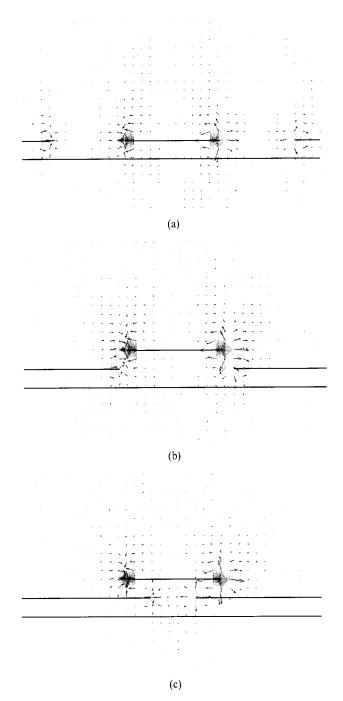

Various characteristic impedances ranging from 40 to 100 ohm are demonstrated with geometrical parameters W/H and S/W as shown in Fig. 5. As S and H increases  $Z_0$  increases when W is fixed. Therefore high  $Z_0$  can be acquired by elevating center strip for a fixed S and W without narrowing the center strip width. The transverse electromagnetic field distributions of a z-directed signal are shown in Fig. 6. Each contour line shows that the equipotential electric field and arrows represent the direction of the electric field vector and the length of arrow is the magnitude of the electric field. As shown in Fig. 6 (a), the fields of conventional CPW are distributed not only in the air but also in silicon substrate. However, the electric fields of ECPW are largely concentrated in the air region, especially in the vicinity metal edges as clearly shown in Fig. 6 (b) and (c). Note that most of electric fields are in the vicinity of air and polyimide in the case of  $S=-20 \mu \,\mathrm{m}$ . It means that the overlapped ECPW line is nearly isolated from the lossy silicon substrate and exhibits low loss characteristic.

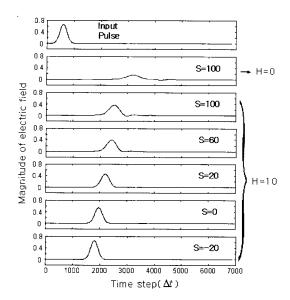

As shown in Fig. 7, it is interesting to observe that how the Gaussian-shaped pulse propagates along the transmission lines of various geometries. The propagating signal on the conventional CPW on  $10 \,\mu$ m-polyimide-loaded silicon is highly distorted and

Fig. 6. Transverse electric field distribution on polyimide-loaded silicon.

- (a) Conventional CPW( $H=0 \mu m$ ,  $S=100 \mu m$ )

- (b) 10  $\mu$  m-elevated CPW( $H=10 \mu$  m,  $S=20 \mu$  m)

- (c) 10  $\mu$  m-elevated CPW( $H=10 \mu$  m,  $S=-20 \mu$  m)

the signal velocity is significantly slower than that of the ECPW cases, thus it is not adequate for high speed circuits. It is clear that ECPW exhibits very low dispersion loss and supports high signal velocity as S varies from  $100 \, \mu \, \text{m}$  to  $-20 \, \mu \, \text{m}$ .

Fig. 7. Waveforms after 4.7 mm propagation for various geometries on  $10\,\mu\,\mathrm{m}$ -polyimide-loaded silicon substrate.  $(\Delta t = 1.36 \times 10^{-14} \text{ sec.})$

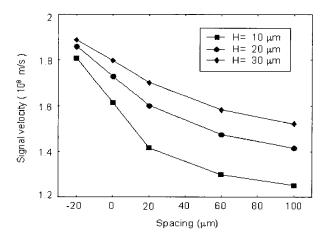

Pulses on the ECPW with  $S=-20 \mu m$  and  $S=0 \mu m$  propagate without any significant distortion and signal integrity is maintained very well. From the fact that the signal velocity of 20  $\mu$  m -overlapped CPW is 1.8 times faster than that of conventional CPW, the ECPW structure can be accepted as a good candidate for high speed interconnects. Elevation height(H) is another critical parameter to characterize the performance of ECPW lines. Signal velocity for elevation heights is shown in Fig. 8. Signal velocity increases as elevation height increases at a fixed spacing. Also signal velocity decreases as spacing increases at a given height.

Fig. 8. Signal velocity along the ECPW line fabricated on standard low-resistivity silicon as a function of spacings and elevation heights.

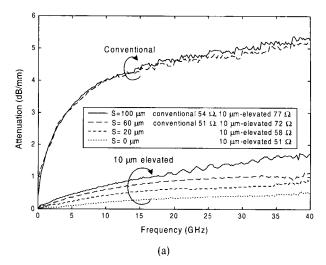

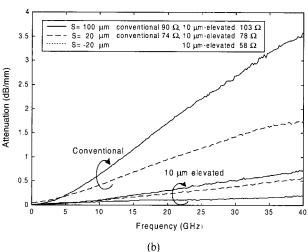

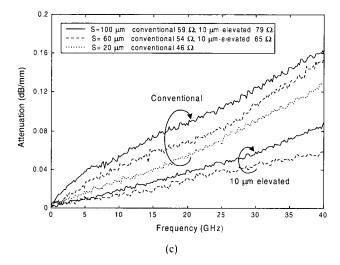

Fig. 9. Measured attenuation for 10  $\mu$  m-elevated CPW on (a) standard low-resistivity silicon(W=100  $\mu$ m)

(b) polyimide-loaded silicon(W=50  $\mu$ m)

(c) polyimide-loaded alumina( $W=100 \mu m$ )

#### IV. Measurement

Attenuation of the fabricated ECPWs with three different substrates are measured using the Network Analyzer and GSG (Ground-Signal-Ground) high frequency coplanar probes. In order to minimize the parasitic effects, on-wafer TRL calibrations are carried out. Measured results are shown in Fig. 9 for three different cases. With the standard low-resistivity silicon the attenuation of the conventional CPW is 5.2 dB at 40 GHz and it is clear that these types of lines can not be used for high-speed circuits. The losses of the  $10\,\mu$ m -ECPWs are 2 dB lower than that of conventional one, and for the  $10\,\mu$ m m-polyimide-loaded silicon the attenuation is significantly reduced at lower frequency region. Note that ECPW with  $S=-20\,\mu$ m reveals the best performance of 0.2 dB below up to 40 GHz. As shown in Fig. 9 (c) the attenuation of ECPW on alumina substrate is about 0.16 dB below.

# V. Conclusion

$10 \,\mu$  m-elevated CPWs are analyzed with 3D-FDTD and on-wafer measured results are presented. The effective dielectric constant, characteristic impedance, electromagnetic field distributions, propagating wave form, signal velocity, and measured total loss are well documented. The effect of elevation heights and spacings are thoroughly studied to characterize the performance of ECPWs. ECPWs on standard silicon have the effect of 3.2 dB attenuation reduction compared with conventional CPW. In the case of polyimide-loaded silicon, attenuation is much lower than that of standard silicon. Particularly, an ECPW with  $S=-20 \mu m$  reveals below 0.2 dB up to 40 GHz. The attenuation of 10  $\mu$  m-polyimide-loaded alumina is below 0.16 dB for conventional case as well as elevated one. This indicates that low-loss alumina substrate imposes much better loss characteristics, even though low-resistivity silicon substrate can be used for high frequency application with center conductor elevation.

#### Seong-Heon Jeong

He received the B.S. degree in Radio Science and Engineering from Korea Maritime University in 2000. He received the M.S. degree in Electrical and Electronics Engineering from Yonsei University in 2002. He is currently a researcher in Samsung Electronics Co., LTD, Korea. His research interests include the electromagnetic computation, RF micro-electro-

mechanical (MEM) devices modeling and wireless communication systems.

#### References

- [1] V. Milanovic, M. Gaitan, E. D. Bowen and M. Zaghloul, "Micromachined Microwave Transmission Lines in CMOS Technology", *IEEE Trans. Microwave Theory and Tech.*, vol. 45, no. 5, May 1997.

- [2] M. Ozgur, et al., "Quasi-TEM Characteristic Impedance of Micromachined CMOS Coplanar Waveguides", *IEEE Trans. Microwave Theory and Tech.*, vol. 48, no. 5, May 2000.

- [3] George E. Ponchak, Alan N. Downey, "Characterization of Thin Film Microstrip Lines on Polyimide", *IEEE Trans. Components, Packaging, and Manufacturing Tech.*, vol. 21, no. 2, May 1998.

- [4] George E. Ponchak, A. Margomenos and Linda P. B. Katehi, "Low-Loss CPW on Low-Resistivity Si Substrates with a Micromachined Polyimide Interface Layer for RFIC Interconnects", *IEEE Trans. Microwave Theory and Tech.*, vol. 49, no. 5, May 2001.

- [5] H. -T. Kim, S. H. Jung, J.-H. Park, C.-W. Baek, Y.-K. Kim and Y.-W. Kwon, "A New Micromachined Overlay CPW Structure With Low Attenuation Over Wide Impedance Ranges and Its Application to Low-Pass Filters", *IEEE Trans. Microwave Theory and Tech.*, vol. 49, no. 9, September 2001.

- [6] H. Ogawa, T. Hasegawa, S. Banda and H. Nakamoto, "MMIC Transmission Lines for Multi-Layered MMICs", IEEE MTT-S Digest. vol. 3, pp. 1067-1070, 1991.

- [7] J.-S. Rieh, L.-H. Lu, L. P. B. Katehi, P. Bhattacharya, E. T. Croke, G. E. Ponchak and S. A. Alterovitz, "X-and Ku-band amplifiers based on Si/SiGe HBT's and micromachined lumped components", *IEEE Trans. Microwave Theory and Tech.*, vol. 46, pp. 685-694, May 1998.

- [8] A. Reichelt, I. Wolff, "New Coplanar-Like Transmission Lines for Application in Monolithic Integrated Millimeter-Wave and Submillimeter-Wave Circuits", *IEEE MTT-S Digest.*, vol. 1, pp. 99-102, 1998.

- [9] Richard E. Matick, Transmission lines for digital and communication Networks, IEEE Press, New York, 1995.

#### Sang-No Lee

He received the B.S. degree from Korea University, in 1998, and M.S degree from Kwangju Institute of Science & Technology, in 2001, respectively. He is currently working toward the Ph.D. degree at Yonsei University. His current research interests include modeling RF-MEMS circuits and designing LTCC-based devices.

#### Sang-Goog Lee

He was born on December 23, 1962. He received the B.E and M.E. degrees in electronics engineering from Inha University in 1988 and 1990, repectively. He received Ph.D. degree in electronics and computer engineering from France Rouen University in 1994. He had been assistant professor in the school of electronics and computer engineering in France Rouen

University and researcher in PSA (Laboratory of Perception, System and Information) at INSA (National Institute of Science and Application) from September 1995 to August 1999. He is project manager of wearable computer project team at SAIT (Samsung Advanced Institute of Technology). His research interests include iMEMS, RFMEMS, Intelligent Sensors, Sensor Data Validation, Wearable Computers and Ubiquitous Computing.

He received the B.S. and M.S. degrees in electronics engineering from Yonsei University in 1987 and 1989, respectively, and the Ph.D. degree from The University of Michigan at Ann Arbor, in 1996. He is currently an Assistant Professor at Yonsei University. His main research interests are in the area of theoretical/numerical electromagnetic modeling and charac-

terization of microwave/millimeter-wave circuits and components, very large scale integration (VLSI) and monolithic-microwave integrated-circuit (MMIC) interconnects, and RF MEMS devices using frequency-and time-domain full-wave methods, and development of numerical techniques for analysis and design of high-speed high-frequency circuits with emphasis on parallel/super computing and wireless communication applications.

#### Yong-Jun Kim

He was born August 28, 1964, in Seoul, Korea. He received the Bachelor of Engineering in electrical engineering from Yonsei Univeristy in 1987. He received the Master of Science in electrical and computer engineering from University of Missouri-Columbia in 1989. During his graduate study in Missouri-Columbia, he worked as a graduate research assistant for Dr.

Russel Pimmel, his advisor. The topic of the research was "Image invariants extraction algorithm using Neural Network".

In 1992, he joined Dr.Mark G. Allen's Microsensors and Microactuators group in Georgia Institute of Technology and conducted research as a graduate research assistant. His research in micromachining includes in-situ measurement of mechanical properties of Polymeric films, integrated inductors, such as meander and solenoid types, and their applications and inductors for high frequency applications. In September 1997, he received his Ph.D. from Georgia institute of Technology. Until September 2000, He researched the general areas of MEMS, integrated RF components and their applications in Samsung Electronics. Currently, He is assistant Professor in school of mechanical engineering, Yonsei university. His current research includes General MEMS, integrated passives for RF of Microwave applications, Micromachining and Electronic Packaging.

#### Han-Kyu Park

He received the B.S. and M.S. degrees in electrical engineering from Yonsei University, Seoul, Korea, in 1964 and 1968, respectively, and the Ph.D. degree in electronic engineering from the Paris VI University, Paris, France, in 1975. Since 1976 he has been teaching in the Department of Electrical and Electronic Engineering at Yonsei University. From 1979 to

1980, he was a Visiting Professor of the Department of Electrical Engineering at Stanford University. From 1985 to 1988, he served as a member of the Technical Committee of the 1988 Seoul Olympics and as a member of the Advisory Committee for 21st Century under direct control of the President from 1989 to 1994. Since 1991, he has been with the G-7 Planning Committee of the Ministry of Trade and Industry. From 1995 to 1996, he was the President of the Korean Institute of Communication Sciences. Since 1993, he has served as Head of the Radio Communications Research Center at Yonsei University. Dr. Park received three Scientific Awards from the Korean Institute of Electrical Engineers in 1976, from the Korean Institute of Telematics and Electronics in 1978, and from the Korean Institute of Communication Sciences in 1986, respectively. His interests include wireless mobile communications, radio technology, communication networks, and optical signal processing.