# The Tripler Differential MMIC Voltage Controlled Oscillator Using an InGaP/GaAs HBT Process for Ku-band Application

Hee-Yong Yoo · Rok-Hee Lee · Bhanu Shrestha · Gary P. Kennedy · Chan-Hyeong Park · Nam-Young Kim

#### **Abstract**

In this paper, a fully integrated Ku-band tripler differential MMIC voltage controlled oscillator(VCO), which consists of a differential VCO core and two triplers, is developed using high linearity InGaP/GaAs HBT technology. The VCO core generates an oscillation frequency of 3.583 GHz, an output power of 3.65 dBm, and a phase noise of -96.7 dBc/Hz at 100 kHz offset with a current consumption of 30 mA at a supply voltage of 2.9 V. The tripler shows excellent side band rejection of 23 dBc at 3 V and 12 mA. The tripler differential MMIC VCO produces an oscillation frequency of 10.75 GHz, an output power of -13 dBm and a phase noise of -89.35 dBc/Hz at 100 kHz offset. \*\*Key words\*\*: Hetero-Junction Bipolar Transistor(HBT), InGaP/GaAs, Voltage-Controlled Oscillator(VCO), Phase Noise, Tripler.

#### I. Introduction

With increasing demand for high speed data rates, the operation frequency of satellite communication systems increases in order to achieve greater bandwidth. Accordingly, high local oscillation(LO) frequency is required for down conversion from RF band to IF band. However, as the oscillation frequency is increased, the quality factor of the resonator is rapidly decreased and the phase noise is increased. Consequently, the signal to noise ratio is decreased and the data transmission error is increased.

We propose a solution to this problem by developing an oscillator using a multiplier. It produces a high oscillation frequency with low phase noise, because it uses the harmonics of the oscillation signal with low phase noise. Phase noise is increased in the ratio of 20 log N with increasing harmonic index  $(N)^{[1]}$ . If the index is 3, the phase noise is increased to 9.4 dB. Therefore, with higher frequency applications, the increment produced by phase noise using the harmonic index is lower than the increment by the Q factor of the resonator. Therefore, combining an oscillator structure with a multiplier is necessary for high frequency band communication systems.

This tripler differential VCO is fabricated using an InGaP/GaAs HBT process. In general, low flicker noise of devices pulls down the phase noise of oscillator. By the way, the flicker noise of an InGaP/GaAs HBT device

is lower than that of other devices such as a GaAs MESFET, GaAs HEMT, etc.<sup>[2]</sup>. So in order to get a low phase noise of oscillator, an InGaP/GaAs HBT process is used in this work.

## II. Circuit Design

The tripler differential VCO consists of a differential VCO core and two triplers. The differential VCO core is designed using an oscillation frequency of 3.583 GHz. The tripler converts the oscillation frequency of 3.583 GHz into an oscillation frequency of 10.75 GHz.

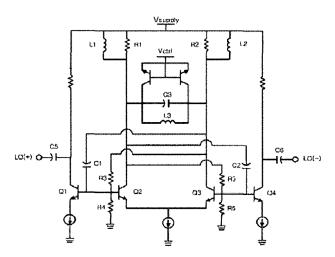

The differential VCO core schematic is shown in Fig. 1. The inductor (L3) in parallel with the capacitor (C3) constitutes a resonator without any other component. The Q value of LC resonator is 14.748. For frequency tuning a varactor diode is implemented by connecting a base configured transistor in parallel with the capacitor (C3). The capacitor contributes 30.25 % of the LC tank and the capacitance variation ratio is 9.24 % of the total capacitance. Thus, the frequency tuning ratio using a variable capacitor is 2.79 % of the resonance frequency, 4.3 GHz. This excludes the parasitic elements of the strip line. So the frequency tuning range is calculated to be around 120 MHz<sup>[3]</sup>.

L1 and L2 control the phase of the active block satisfying the Barkhausen criterion at the oscillation frequency. In order to control the output power, R1 and R2 are used. If these values are increased, the voltage

signal swing at the collector of Q2 and Q3 is increased [4]. C1 and C2 are cross coupled capacitors, which make a positive feedback loop at the oscillation frequency. Q2 and Q3 generate a balanced signal using a switching operation. In this paper, the common emitter (CE) drive stage (Q1 and Q4) are used to provide enough power for the tripler<sup>[8]</sup>. The base of Q1 and Q4 is connected with the base of Q2 and Q3 in order to provide the base bias. If the base bias of Q1 and Q4 is provided by the collector of VCO core, the large output voltage swing of CE amplifier required for the tripler can not be obtained due to the small voltage headroom of Q1 and Q4.

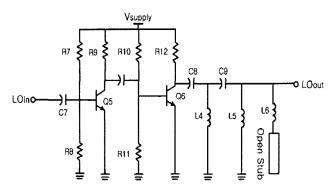

The tripler employs a 2 stage amplifier as shown in Fig. 2. The first stage (Q5) and second stage (Q6) are the common emitter configuration and are optimized to provide maximum power for the third order harmonic in class B operating mode. The input of tripler is provided by VCO core through C1 and C2 in Fig. 1.

The third oder harmonic of this differential tripler VCO is output frequency. So all harmonics excepted third oder harmonic have to be removed for increasing the linearity of tripler VCO. At first, in order to suppress the fundamental and the second order harmonics, the output block of the third stage is configured with a high pass filter which has a cut-off frequency of 7 GHz. In addition to low frequency band suppression, the gradual decrease in harmonic amplitude (for the 4th and 5th harmonics) results in an output spectrum. Therefore it is similar to the band pass filter with the third order harmonic as the center frequency.

Furthermore, to obtain greater linearity, a miniaturized open stub was used. Generally an open stub acts as a capacitor with a parasitic inductance which depends on the line length of the open stub. Therefore, an open stub

Fig. 1. Schematic of the differential VCO core.

Fig. 2. Schematic of the tripler.

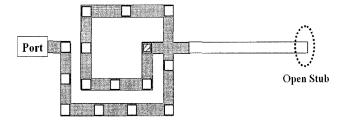

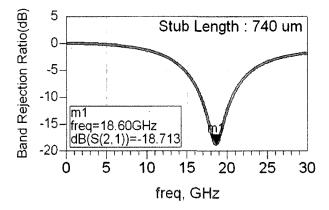

can be operated as band stop filter(BSF). But, generally for the open stub to act as a BSF in low frequency applications, a long line length is required to obtain a large inductance. Thus, in this paper a spiral inductor is connected in series with the open stub to obtain a BSF. This BSF suppresses the fifth harmonic which decreases the linearity of the tripler VCO. A diagram of the designed open stub with parasitic inductance plus its simulation results are shown in Figs. 3 and 4. As a result of combining an open stub and an inductor, length of the open stub shown in Fig. 2 can be shorten by a quarter as compared to a conventional one. Moreover, it can not only increase the linearity but also suggest the opportunity realizing the open stub under 20 GHz in MMIC.

Fig. 3. Structural diagram of the designed open stun acting as a BSF.

Fig. 4. Simulation result of open stub.

#### III. Fabrication and Measurement

The differential VCO core operates with a supply voltage of 2.9 V and current consumption of 30 mA. Similarly, the triplers operate with a supply voltage of 3 V and current consumption of 12 mA. A spectrum analyzer (Agilent E4440A) and a signal generator (Agilent 83650B) were used for measurement. The baluns which were designed using a hybrid coupler (rat race), were used to measure a balanced output signal of 3.58 GHz and 10.75 GHz.

The VCO core die and the tripler VCO die were attached to the PCB using silver epoxy. The tripler differential VCO with passive balun is shown in Fig. 5. In this device, DC contact was made using gold wire bonding with an approximate length of 10 mil and a diameter of 1 mil.

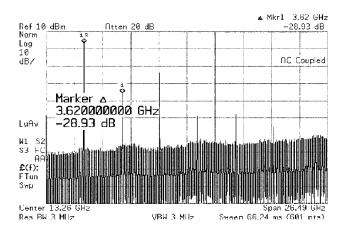

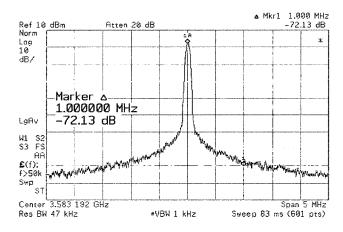

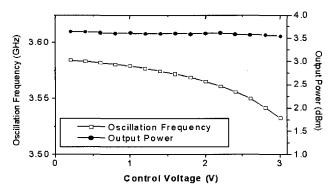

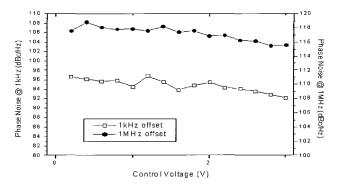

The VCO core output is measured by utilizing a 3.583 GHz balun as shown in Fig. 6. The output power of the fundamental harmonic is 3.65 dBm, and the difference between the first and the second harmonics is 28 dBc. Fig. 7 shows a frequency spectrum measurement of the differential VCO core with a center frequency of 3.583 GHz, the span of 5 MHz, and a resolution bandwidth(RBW) of 47 kHz. Phase noises of -96.8 dBc/Hz and -118.8 dBc/Hz were obtained at offset frequencies of 100 kHz and 1 MHz respectively. From Table 1, the simulated oscillation frequency is about 200 MHz higher than the measured frequency. It is thought that the difference between simulation and measurement lies in the use of the base-emitter connected transistor model during simulation; this model may not be accurate enough. So, the oscillator was designed using a frequency as high as 200 MHz, and the desired oscillation frequency was achieved in line with the predicted frequency margin. The output power and phase noise characteristics are constant within the frequency tuning range as a depicted in Fig. 8 and Fig. 9. Frequency tuning was obtained using  $V_{ctrl}$  without the need

Fig. 5. The tripler differential VCO with passive balun.

Table 1. A comparison of simulation and measurement results from the differential VCO core.

| Items                                |                   | Unit               | Simulation<br>Results | Measurement<br>Results |

|--------------------------------------|-------------------|--------------------|-----------------------|------------------------|

| Oscillation Frequency                |                   | GHz                | 3.8                   | 3.583                  |

| Output Power                         |                   | dBm                | 6                     | 3.23~3.65              |

| Tuning Range (0~3.5 V)               |                   | MHz                | 180                   | 143                    |

| Supply Voltage                       |                   | V                  | 3                     | 2.9                    |

| Current Consumption                  |                   | mA                 | 35                    | 30                     |

| Phase<br>Noise                       | 100 kHz<br>offset | dBc/Hz             | -                     | -96.7                  |

|                                      | 1 MHz<br>offset   |                    | -                     | -118.85                |

| Frequency Drift as<br>Supply Voltage |                   | MHz                | -                     | 55                     |

| Chip Size                            |                   | $\mu \mathrm{m}^2$ | 995×850               | 995×850                |

Fig. 6. Second harmonic suppression of the differential VCO core.

Fig. 7. Frequency spectrum measurement of the differential VCO core.

Fig. 8. Variation of output frequency and output power with VCO control voltage.

for any additional circuit (Fig. 1). The usable frequency range is from 3.53 GHz to 3.57 GHz.

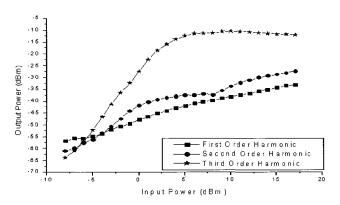

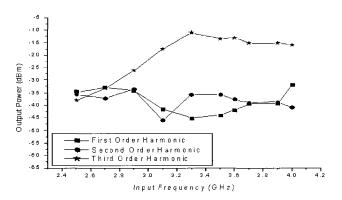

The tripler was measured using an input balun (3.58 GHz) and output balun (10.75 GHz). A signal generator was connected to the input port and the tripler output characteristic was measured with an ideal input signal. Fig. 10 shows output power versus input power characteristics, with a third order harmonic output power of over -13 dBm at an input power of 5 dBm. Therefore, the output power is fixed at about -10 dBm, since the power loss in the balun is considered. Furthermore, the output power specification of the differential oscillator (which drives the double balanced mixer) is satisfied. Also the output power as a function of input frequency variation  $(2.5 \sim 3.9 \text{ GHz})$  is shown in Fig. 11. From this Figure, the optimum input power level is 5 to 7 dBm with an excellent second harmonic rejection figure of over 23 dBc.

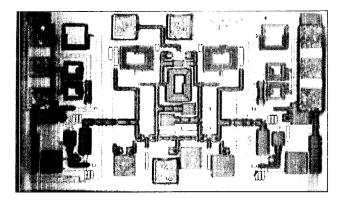

The tripler chip size is  $470 \times 850~\mu\,\mathrm{m}^2$  and has an output frequency of 10.75 GHz. It is smaller than any other tripler ever reported in the literature and it has the lowest application frequency. Therefore, this tripler can be implemented within the differential VCO to form a tripler differential VCO; this can be used as a component in a phase locked loop(PLL). These comparisons are shown in Table 2.

A microphotograph of the on-chip tripler differential

Table 2. A comparison of chip size with frequency obtained from the literature.

| No. | Rejection of $2f_0$ (dBc) | Frequency<br>(GHz) | Chip Size ( $\mu$ m <sup>2</sup> ) | Reference |

|-----|---------------------------|--------------------|------------------------------------|-----------|

| 1   | Unknown                   | 48                 | 1490×1300                          | [5]       |

| 2   | 18                        | 38                 | 1500×2000                          | [6]       |

| 3   | 11~40                     | 25.5~31.5          | 1150×2500                          | [7]       |

| 4   | 25                        | 10.75              | 470×850                            | This work |

Fig. 9. Phase noise as a function of VCO control voltage.

Fig. 10. Output power of the tripler as a function of input power at 3.583 GHz.

Fig. 11. Output power of the tripler as a function of input frequency at input power of 5 dBm.

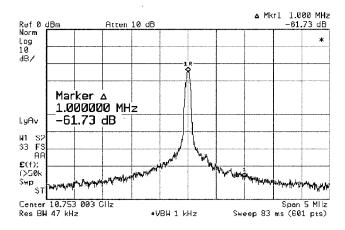

VCO is shown in Fig. 12. The output power and the phase noise characteristics of the tripler differential VCO are shown in Fig. 13. When the spectrum analyzer is set at the center frequency of 10.75 GHz, with a span of 5 MHz and an RBW of 47 kHz, an output power of -13 dBm is observed at 10.75 GHz.

Also, the phase noise is -89.35 dBc/Hz at an offset frequency of 100 kHz and -108 dBc/Hz at offset frequency of 1 MHz. A comparison of the phase noise of the tripler differential VCO and a differential VCO core is shown in Table 3. The difference in phase noise

Fig. 12. A microphotograph of the on-chip tripler differential VCO(chip size: 1,400×850  $\mu$  m<sup>2</sup>).

Fig. 13. Output power and phase noise characteristics of the tripler differential VCO.

Table 3. A comparison of the phase noise from the differential VCO core and the harmonic differential VCO.

| Offset    | Phase Noise              |                             |  |

|-----------|--------------------------|-----------------------------|--|

| Frequency | Differential<br>VCO Core | Tripler<br>Differential VCO |  |

| 100 kHz   | -96.7 dBc/Hz             | -89.35 dBc/Hz               |  |

| 1 MHz     | -118.85 dBc/Hz           | -108.45 dBc/Hz              |  |

between the two is 10.4 dB, which is similar to the calculated value of 9.4 dB.

## IV. Conclusion

A tripler differential VCO operating in the Ku-band was implemented by multiplying the fundamental oscillation frequency from an S-band VCO. For the good phase noise, it consists of a differential VCO core with

low phase noise characteristic and two triplers, which are the smallest compared with any other conventional triplers. Also the linearity of triplers is improved by the miniaturized open stub. As a result, the performance of a fabricated tripler differential VCO using the suggested techniques, the two triplers with an open stub to improve the linearity is desirable for Ku-band application.

This work has been performed through the Support Project of Mission Telecom Co.(MTC) and University Information Technology Research Center(ITRC) supported by the Ministry of Information & Communication of Korea. Also, the authors would like to thank Knowledge\*on Inc. for the fabrication of the tripler differential MMIC VCO using its 6 inch In-GaP/GaAs HBT foundry service and design library.

#### References

- [1] Edmar Camargo, Design of FET Frequency Multipliers and Harmonic Oscillators, Artech House, Boston, pp. 8-9, 1998.

- [2] W. J. Ho, "GaAsP/GaAs HBT's for high-speed integrated circuit application", *IEEE Tran. Electron Devices*, vol. 40, pp. 2113-2114, Jun. 1993.

- [3] Behzad Razavi, *RF Microelectrnics*, Prentice Hall, p. 231, 1998.

- [4] Jan Craninckx, "Low-noise voltage-contolled oscillators using enhanced LC-tanks", *IEEE Tran. Circuits and Systems*, vol. 42, pp. 794-804, Dec. 1995.

- [5] A. Orzati, F. Robin, H. P. Mier, O. J. Homan, and W. Bachtold, "A 48 GHz monolithically integrated frequency tripler with InP HEMTs", *Indium Pho*sphide and Related Materials Conference, pp. 447-450, May 2002.

- [6] A. Boudiaf, D. Bachelet, and C. Rumelhard, "A high-efficiency and low-phase-noise 38-GHz pHEMT MMIC tripler", *IEEE Tran. Microwave Theory and Techniques*, vol. 48, pp. 2546-2553, Dec. 2000.

- [7] Beaulieu, C., "Millimeter wave broadband frequency tripler in GaAs/InGaP HBT technology", *IEEE MTT-S International Microwave Symposium Digest.*, vol. 3, pp. 1581-1584, Jun. 2000.

- [8] Jae-Young Lee, B. Shrestha, J. Y. Lee, S. J. Kim, J. C. Lee, B. J. Lee, J. H. Kim, S. H. Jeon, and N. Y. Kim, "InGaP/GaAs HBT MMIC VCDRO with wide tuning range and low phase noise", Asia Pacific Microwave Conference, Dec. 2004.

## Hee-Yong Yoo

He was born in Korea in 1978. He received the B.S. and M.S. degrees in electronic engineering from Kwangwoon University, Seoul, Korea, in 2003 and 2005, respectively. His main interests are RF/MMIC system design technologies.

## Gary P. Kennedy

He received the B.S. degree in Applied Physics from Liverpool John Moores University in 1988 and the Ph.D. degree in Solid State Physics/Micro-electronics from the University of Liverpool in 1993. After completing his studies, he worked as a researcher and Research Fellow in the Universities of Liverpool and Southampton, respectively.

In January 2000, he began working as a Reliability Engineer at European Semiconductor Manufacturing Ltd., UK. He is currently working as a Research Professor in the ITRC RFIC Center of Kwangwoon University. His main research field is SiGe RFIC.

#### Rok-Hee Lee

He was born Haenam, Korea in 1977. He received the B.S. and M.S. degrees in electronic engineering from Kwangwoon University, Seoul, Korea, in 2004 and 2006, respectively. His main interests are RF/MMIC system design technologies.

### Chan-Hyeong Park

He received the B.S., M.S., and Ph.D., degrees in electronics engineering from Seoul National University in 1992, 1994, and 2000 respectively. He was a visiting scientist of Research Laboratory of Electronics at Massachusetts Institute of Technology between 2000 and 2003. He has been a Full-time Lecturer and Assistant

Professor in the dept. of electronics and communications Engineering at Kwangwoon University. His current interests are modelling and simulation of noise in semiconductor devices and CMOS radio-frequency integrated circuits and nanoscale devices.

## Bhanu Shrestha

He was born in Dolakha, Nepal in 1966. He received the B.S. and M.S. degrees in electronic engineering from Kwangwoon University, Korea in 1999 and 2004, respectively. At present, he is studying in Ph.D. degree in the same Univ. He is a member of Nepal Engineering Council(NEC), Nepal Engineers' Association(NEA), and

Korea Electromagnetic Engineering Society(KEES) since 1999, 2002, and 2004, respectively, and also a student member of IEEE since 2004. His main interested fields of research are RFIC/MMIC/RFID circuits and system design.

## Nam-Young Kim

He was born in Korea in 1960. He received the B.S. degree in electronic engineering from Kwangwoon University, the M.S. and the Ph.D. degrees from State Univ. of New York at Buffalo. He was a research scientist of CEEM at SUNY at Buffalo in 1994. Since September 1994, he has been an Professor in the Dept. of

electronic engineering at Kwangwoon Univ. He has been the director of RFIC Center since March 1998. His research fields are in the areas on semiconductor device modeling, ASIC, RFIC and MMIC design.