# CMOS Linear Power Amplifier with Envelope Tracking Operation

(Invited Paper)

Byungjoon Park<sup>1</sup> · Jooseung Kim<sup>2</sup> · Yunsung Cho<sup>1</sup> · Sangsu Jin<sup>2</sup> · Daehyun Kang<sup>3</sup> · Bumman Kim<sup>2,\*</sup>

# **Abstract**

A differential-cascode CMOS power amplifier (PA) with a supply modulator for envelope tracking (ET) has been implemented by 0.18 µm RF CMOS technology. The loss at the output is minimized by implementing the output transformer on a FR-4 printed circuit board (PCB). The CMOS PA utilizes the 2<sup>nd</sup> harmonic short at the input to enhance the linearity. The measurement was done by the 10 MHz bandwidth 16QAM 6.88 dB peak-to-average power ratio long-term evolution (LTE) signal at 1.85 GHz. The ET operation of the CMOS PA with the supply modulator enhances the power-added efficiency (PAE) by 2.5, to 10% over the stand-alone CMOS PA for the LTE signal. The ET PA achieves a PAE of 36.5% and an ACLR<sub>E-UTRA</sub> of —32.7 dBc at an average output power of 27 dBm.

Key Words: CMOS, Envelope Tracking, Long-Term Evolution, Power Amplifier, Supply Modulator.

# I. Introduction

The smartphone market has increased dramatically as smartphones have become an essential product in modern life. The increases in user demand for high quality service have prompted the evolution of wireless communication systems that can handle enormous amounts of data, which has required increased power consumption, efficient circuits, and large capacity batteries. The circuit cost and size are important parameters, so much research has been directed towards reducing the cost and size of smartphone elements. Among these elements, the front-end module is the bottleneck for these reductions. In this paper, we focus on radio frequency (RF) circuit systems and particularly on RF power amplifiers (PA).

Most of the chips in a smartphone are now being inte-

grated into a single chip to reduce the size and cost. However, modifications to the RF power amplifier are lagging. Reliability and performance issues have led to the use of a gallium arsenide (GaAs) substrate for RF PA, whereas other chips are based on a CMOS substrate. The GaAs substrate has limited integration capability and high cost compared to the CMOS substrate; therefore, PAs will eventually be integrated into either a CMOS substrate with RFICs or a silicon-on-insulator (SOI) process with switches, for low cost and small size.

Silicon substrates have the drawbacks of a low breakdown voltage, no back via to the ground, a high knee voltage, and a large substrate loss. Even if the SOI process overcomes the substrate loss issue with a high-resistivity insulator beneath the buried oxide, the other issues must be taken care of at the circuit level, as in the bulk CMOS process [1, 2]. A

Manuscript received January 22, 2014; Revised February 17, 2014; Accepted February 19, 2014. (ID No. 20140122-01J)

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>&</sup>lt;sup>1</sup>Division of Information Technology Convergence Engineering, Pohang University of Science and Technology (POSTECH), Pohang, Korea.

<sup>&</sup>lt;sup>2</sup>Department of Electrical Engineering, POSTECH, Pohang, Korea.

<sup>&</sup>lt;sup>3</sup>Broadcom Corporation, Matawan, NJ, USA.

<sup>\*</sup>Corresponding Author: Bumman Kim (e-mail: bmkim@postech.ac.kr)

<sup>©</sup> Copyright The Korean Institute of Electromagnetic Engineering and Science. All Rights Reserved.

cascode structure provides a solution for a low breakdown voltage [3, 4]. A differential structure creates a virtual ground point and releases the source degeneration effect by a source-to-ground bonding wire [5]. The use of an output transformer helps to handle the substrate issues and the voltage combination also increases the output load impedance of transistors. The further improvement in the performance is achieved by the use of the appropriate harmonic tuning method described in this paper.

In addition to reducing the size and cost, improving the efficiency of the PA is also a hot issue. The PAs should handle the signals with wide channel bandwidth and high peakto-average power ratio (PAPR) since the wireless communication systems, such as long-term evolution (LTE), operate using high data rate signals. The high PAPR of the signals reduces the efficiency of the PAs at a low average output power region because the fixed supply voltage and the output load are optimized for the peak instant power.

Several techniques can enhance the efficiency of PA for high PAPR applications. The Doherty technique modulates the load impedance using a quarter-wavelength transformer for both the back-off power and the peak power [6]. A reconfigurable output matching network, according to the power level, is also a good candidate for high PAPR signals [7]. However, these techniques require complex output matching networks, which have a large loss and are sensitive to a bandwidth. Envelope elimination and restoration (EER) and envelope tracking (ET) improve the efficiency by modulating the PA supply voltage. Conventional EER structures are nonlinear due to delay mismatch between the amplitude and the phase path, and further, they run into a leakage problem due to a large input power injection even for a low output operation [8]. The ET technique is less sensitive to the delay mismatch [9], and enables a linear operation by utilizing a linear PA and supply modulator without additional linearization technique [10] to improve the efficiency of the PA.

The organization of this paper is as follows. Section  ${\rm I\hspace{-.07cm}I}$  describes the harmonic control for the highly linear CMOS PA. Section  ${\rm I\hspace{-.07cm}I}$  shows the configuration of a hybrid switching supply modulator. Section  ${\rm I\hspace{-.07cm}V}$  focuses on the ET operation by combining the supply modulator and the CMOS PA. Implementation and measured results are shown in Section  ${\rm V}$ .

## II. HARMONIC CONTROL FOR LINEAR CMOS PA

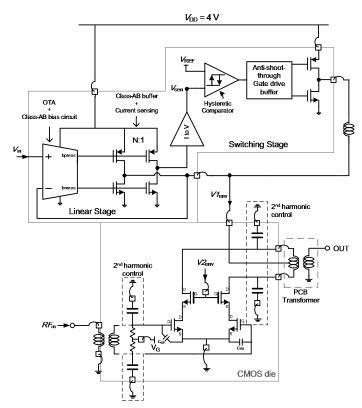

Fig. 1 shows the schematic design of the CMOS PA with the hybrid supply modulator [10]. The basic structure of the PA is a differential-cascode structure that uses a transformer at the output [10-13]. This structure alleviates the drawbacks of the CMOS substrate. The performance is enhanced by designing the output transformer on a FR-4 printed circuit board (PCB) to minimize the loss. The  $2^{\rm nd}$  harmonic short circuits are also applied at the input and output. Here, we have concentrated on the effects on the  $2^{\rm nd}$  harmonic.

Fig. 1. Schematic of CMOS power amplifier with envelope tracking supply modulator. RF = radio frequency, PCB = printed circuit board, OTA = operational transconductance amplifier.

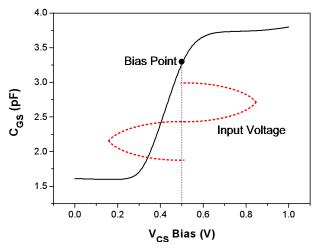

Many nonlinear components exist in a CMOS PA. As discussed in [14],  $C_{\rm GS}$  contributes the most to linearity performance. Thus, compensating the  $C_{\rm GS}$  nonlinearity is essential for improving the performance. The capacitance between the gate and source of the transistor increases as the voltage level increases across the two terminals, as shown in Fig. 2.

The RF PA gate bias is located in a class-AB mode. Fig. 2 shows the input voltage swing at the class-AB bias point,

Fig. 2. Variation of the gate to source capacitance.

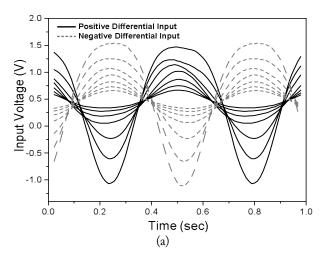

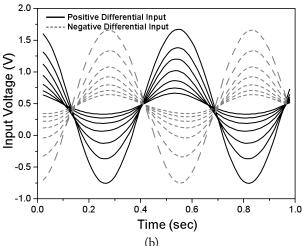

Fig. 3. Simulated waveforms of input voltage according to input power levels: (a) without 2<sup>nd</sup> harmonic short and (b) with 2<sup>nd</sup> harmonic short.

together with C<sub>GS</sub> variation. As clearly shown, the bias point is located where the C<sub>GS</sub> varies rapidly. Therefore, the upper part of the input voltage and the lower part experience different capacitances and generate an asymmetric waveform, as plotted in Fig. 3(a). This asymmetric waveform is mainly due to the 2<sup>nd</sup> harmonic component that is generated by the nonlinear C<sub>GS</sub>. Therefore, by applying the 2<sup>nd</sup> harmonic short circuit at the input, we can easily compensate the C<sub>GS</sub> nonlinearity and achieve a symmetric waveform, as shown as Fig. 3(b). This symmetrical signal is especially important in a differential structure. This provides the proper virtual ground at the common source node of CS amplifiers, making a proper source ground. Additionally, this short eliminates the 2<sup>nd</sup> harmonic that is fed back to the input, which generates a memory effect. If not terminated, the 2<sup>nd</sup> harmonics can be mixed with the fundamental frequency signal, thereby creating the source of the asymmetry third-order intermodulation distortion (IMD3). Therefore, the 2<sup>nd</sup> harmonic short at the input is a very important linearizing element for a differential linear PA.

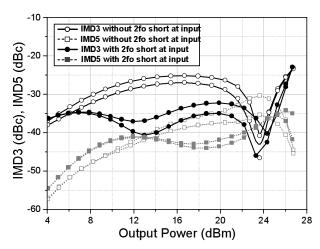

Fig. 4. Simulated comparisons of third-order intermodulation distortion (IMD) between the power amplifiers with and without the 2<sup>nd</sup> harmonic short at the input.

This effect was verified by carrying out a simulation. Two circuits are designed with and without input of the 2<sup>nd</sup> harmonic short. Both circuits are simulated with an output 2<sup>nd</sup> harmonic short and an ideal transformer. Fig. 4 shows the IMD curves with the 2<sup>nd</sup> harmonic short at the input, which clearly describes the effect of C<sub>GS</sub> nonlinearity compensation. The IMD at the mid-power region is significantly reduced. Although the IMD at the high-power region is mainly generated by the nonlinearity caused by the voltage and current saturation [11], the linear output power, satisfying IMD3 below —30 dBc, has been increased by about 0.5 dB.

#### III. HYBRID SUPPLY MODULATOR DESIGN

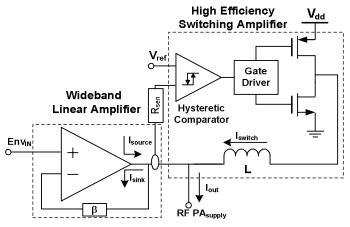

A supply modulator is employed to modulate the drain bias of the RF PA for enhanced efficiency. Maximum efficiency of the ET system depends on the efficiency of both the PA and the supply modulator. In [15, 16], a low dropout regulator is employed as the supply modulator. It operates over a wide bandwidth, but is not efficient enough for high PAPR signals. In [17, 18], a switched-mode power supply (SMPS) delivers high efficiency, but its bandwidth is too narrow to use in 4G systems, such as Mobile-WiMAX and 3GPP LTE. In [19-21], a hybrid switching converter that combines the advantages of the two modulators is used to achieve high efficiency and good linearity simultaneously as shown in Fig. 5. In this architecture, the switching converter operates slowly as a quasi-constant current source, compared to a conventional SMPS, while the wideband linear regulator regulates the output voltage and compensates the ripple current of the switching converter. A control stage, which is composed of a current sensing circuit and a hysteretic comparator, changes the states of the switching converter according to the polarity and magnitude of the sensed current from the linear regulator to output.

Fig. 5. Simplified block diagram of the hybrid supply modulator. RF = radio frequency, PA = power amplifier.

The wideband linear regulator operates as a voltage-controlled voltage source. This means the output voltage of the linear amplifier is the same as its input voltage due to its high gain, wide bandwidth, and negative feedback loop. As introduced in [21], a folded-cascode operational transconductance amplifier (OTA) is used as a gain stage to achieve a large bandwidth and a high DC gain. A large current driving capability and a rail-to-rail operation are obtained by an output buffer with a common source configuration, and it is biased at a class-AB for linearity and efficiency. The switching converter operates as a dependent current source. Generally, the average switching frequency is dependent on the hysteresis width, inductor value, and some other parameters for a narrowband signal.

The average switching frequency for a wideband signal is mainly determined by its bandwidth. The size of the power switch is determined by considering the conduction loss and switching loss at the specific load resistance. The protection, high efficiency, and low switching noise of the switches are obtained by using an anti-shoot-through circuit [22]. A gate driver for the anti-shoot-through switching converter turns on/off the two power transistors and can be designed easily using four MUXs and inverter chains [23].

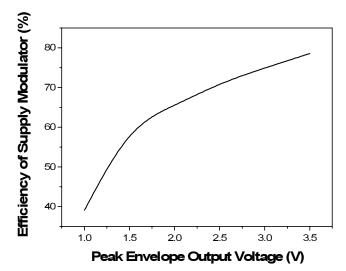

The linear regulator determines the bandwidth of the supply modulator. The linear regulator of the designed supply modulator delivers a gain-bandwidth product of greater than 70 MHz and a DC gain of more than 50 dB with a stable operation. The dynamic output voltage swing range is from 0.9 to 3.5 V. The 0.9 V is the envelope shaping offset to prevent the operation below the knee voltage, and the 3.5 V is the peak envelope output voltage for a reliable operation of the CMOS RF PA. Fig. 6 shows a simulated efficiency of the supply modulators with a variable load. The variable load is a real PA model based on a class-AB biased PA and is realized by a voltage-controlled current source, as introduced in [21]. A 10-MHz LTE signal with a PAPR of 6.88 dB has a simulated efficiency of 78.5% at the peak power.

Fig. 6. Simulated efficiency of the supply modulator.

#### IV. CMOS PA WITH ENVELOPE TRACKING OPERATION

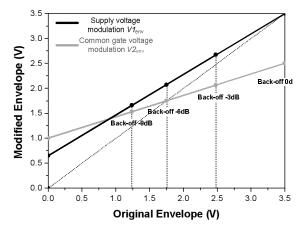

The PA under ET operation experiences large amplitude-to-amplitude modulation (AM/AM) and amplitude-to-phase modulation (AM/PM) distortions under a low supply voltage, since the input/output capacitance variations and the knee voltage effect are increased. Thus, the envelope signal is reshaped as shown in Fig. 7. The minimum voltage from the supply modulator is set to 0.65 V, and the envelope shape is decided according to the power level. Proper operation of the PA should be ensured by modulation of the gate of the common gate (CG) transistor as shown in the Fig. 7, to make the common source (CS) transistor and CG transistor stay in the saturation mode [4]. The envelope-shaping ensures that the PA operates at the IMD sweet spot tracked by the envelope of the signal, and the overall IMD is improved.

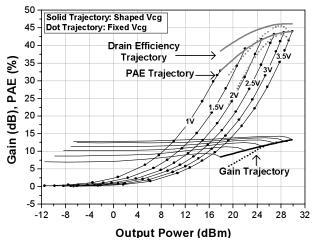

Fig. 8 shows the measured continuous wave performance of the PA at 1.85 GHz by sweeping the drain voltage from 1.0 to 3.5 V and the CG bias from 1.45 to 2.51 V. The

Fig. 7. Envelope-shaping for the voltages of the drain and the gate of the common-gate transistor.

Fig. 8. Measured continuous wave performance of the power amplifiers sweeping the drain voltage from 1 to 3.5 V with the common gate (CG) bias  $V_{CG}$  swing from 1.45 to 2.51 V and fixed  $V_{CG}$ . PAE = power-added efficiency.

drain efficiency (DE), power-added efficiency (PAE), and gain of the PA for the LTE signal under ET operation are expected to follow the DE, PAE, and gain trajectories, respectively, as shown in the figure. For the sake of comparison, the performance for a fixed bias at the gate of the CG transistor is also plotted. The efficiency and the linearity are very poor for the fixed bias case. These data show that the properly shaped envelope shaping should also be supplied to the gate of the CG transistor for the ET operation with a cascode CMOS PA structure. The envelope shaping shown in Fig. 7 is optimized for the LTE signal at an output power of 27 dBm as well as at the back-off regions. In this way, the efficiency is improved significantly at a low power region.

#### V. IMPLEMENTATION AND EXPERIMENTAL RESULTS

The linear differential CMOS PA and ET supply modulator are fabricated on a 0.18-µm RF CMOS technology. Both chips are mounted on a FR-4 PCB. The output transformer is printed on the same board, having 0.5 dB loss. All inductors to resonate out the 2<sup>nd</sup> harmonics are realized by bonding wires to minimize the loss.

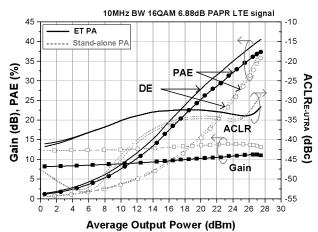

Fig. 9 shows the measured performance of the ET PA and the stand-alone PA at 1.85 GHz for a 10-MHz bandwidth 16QAM 6.88 dB PAPR LTE signal. The performance of the stand-alone PA with a supply voltage of 3.5 V results in a PAE of 34.0% and an ACLR<sub>E-UTRA</sub> of -30 dBc at an average output power of 27 dBm. The ET operation of the CMOS PA with the supply modulator enhances the PAE by 2.5% to 10% over the stand-alone CMOS PA for the LTE signal. The ET PA achieves a PAE of 36.5% and an ACLR<sub>E-UTRA</sub> of -32.7 dBc at an average output power of 27 dBm. Both the efficiency and linearity have been improved by ET operation. The measured average efficiency of the supply modulator under the LTE test is

Fig. 9. Measured performance of the envelope tracking power amplifier (ETPA) and the stand-alone PA for a 10-MHz bandwidth 16QAM 6.88 dB peak-to-average power ratio long-term evolution signal. PAE = power-added efficiency, DE = drain efficiency, ACLR = adjacent channel leakage ratio.

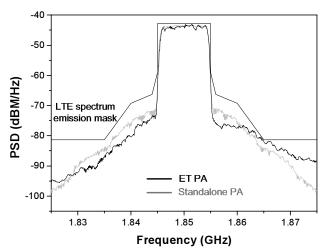

Fig. 10. Measured spectra of the power amplifier (PA) at an output power of 27 dBm for the long-term evolution (LTE) signal. ET = envelope tracking, PSD = power spectral density.

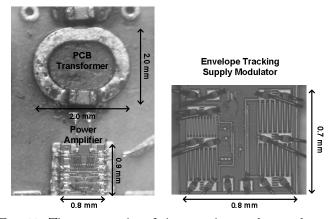

Fig. 11. The micrographs of the test chips and printed circuit board (PCB) transformer.

73%.

Fig. 10 depicts the measured spectra of the PAs at an output power of 27 dBm for the LTE signal. The AC-LR<sub>E-UTRA</sub> is measured with a 9-MHz resolution bandwidth at both a center frequency and a 10-MHz offset and its specification is -30 dBc. Fig. 11 shows the micrographs of the supply modulator chip, the PA chip, and the PCB transformer. The total chip area sizes of the PA and supply modulator are 0.8 mm  $\times$  0.9 mm and 0.8 mm  $\times$  0.7 mm, respectively.

## VI. CONCLUSIONS

A differential-cascode CMOS PA with supply modulator has been implemented by 0.18  $\mu m$  RF CMOS technology. The importance in compensating the  $C_{GS}$  has been described. The solution uses a  $2^{nd}$  harmonic short circuit. The efficiency of the PA system is improved by the introduction of a basic ET supply modulator. The supply modulator and the harmonic control on the PA help the ET PA to achieve a PAE of 36.5% and an ACLR<sub>E-UTRA</sub> of  $-32.7\,dBc$  at an average output power of 27 dBm.

This research was supported by the MSIP (Ministry of Science, ICT & Future Planning), Korea in the ICT R&D Program 2013.

#### REFERENCES

- [1] D. Chowdhury, C. D. Hull, O. B. Degani, Y. Wang, and A. M. Niknejad, "A fully integrated dual-mode highly linear 2.4 GHz CMOS power amplifier for 4G WiMAX applications," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 12, pp. 3393–3402, Dec. 2009.

- [2] A. Afsahi, A. Behzad, and L. E. Larson, "A 65 nm CMOS 2.4 GHz 31.5 dBm power amplifier with a distributed LC power-combining network and improved linearization for WLAN applications," in *IEEE International Solid-State Circuits Conference Digest of Technical Papers*, San Francisco, CA, 2010, pp. 452–453.

- [3] T. Sowlati and D. M. W. Leenaerts, "A 2.4-GHz 0.18µm self-biased cascode power amplifier," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 8, pp. 1318–1324, Aug. 2003.

- [4] D. Kang, B. Park, D. Kim, J. Kim, Y. Cho, and B. Kim, "Envelope-tracking CMOS power amplifier module for LTE applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 61, no. 10, pp. 3763–3773, Oct. 2013.

- [5] I. Aoki, S. D. Kee, D B. Rutledge, and A. Hajimiri, "Fully integrated CMOS power amplifier design using the distributed active-transformer architecture," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 3, pp. 371–383, Mar. 2002.

- [6] E. Kaymaksut and P. Reynaert, "Transformer-based un-

- even Doherty power amplifier in 90 nm CMOS for W-LAN applications," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 7, pp. 1659–1671, Jul. 2012.

- [7] H. Hedayati, M. Mobarak, G. Varin, P. Meunier, P. Gamand, E. Sanchez-Sinencio, and K. Entesari, "A 2-GHz highly linear efficient dual-mode BiCMOS power amplifier using a reconfigurable matching network," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 10, pp. 2385 2404, Oct. 2012.

- [8] D. K. Su and W. J. McFarland, "An IC for linearizing RF power amplifiers using envelope elimination and restoration," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 12, pp. 2252–2258, Dec. 1998.

- [9] F. Wang, D. F. Kimball, D. Y. Lie, P. M. Asbeck, and L. E. Larson, "A monolithic high-efficiency 2.4-GHz 20dBm SiGe BiCMOS envelope-tracking OFDM power amplifier," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 6, pp. 1271–1281, Jun. 2007.

- [10] D. Kang, B. Park, C. Zhao, D. Kim, J. Kim, Y. Cho, S. Jin, H. Jin, and B. Kim, "A 34% PAE, 26-dBm output power envelope-tracking CMOS power amplifier for 10-MHz BW LTE applications," in *IEEE International Microwave Symposium*, Montreal, Canada, 2012.

- [11] B. Park, D. Kang, D. Kim, Y. Cho, C. Zhao, J. Kim, Y. Na, and B. Kim, "A 31.5% 26 dBm LTE CMOS power amplifier with harmonic control," in *Proceedings of the 7th European Microwave Integrated Circuits Conference*, Amsterdam, The Netherlands, 2012, pp. 341–344

- [12] S. Jin, M. Kwon, K. Moon, B. Park, and B. Kim, "Control of IMD asymmetry of CMOS power amplifier for broadband operation using wideband signal," *IEEE Transactions on Microwave Theory and Techniques*, vol. 61, no. 10, pp. 3753-3762, Oct. 2013.

- [13] S. Jin, B. Park, K. Moon, M. Kwon, and B. Kim, "Linearization of CMOS cascode power amplifiers through adaptive bias control," *IEEE Transactions on Microwave Theory and Techniques*, vol. 61, no. 12, pp. 4534 – 4543, Dec. 2013.

- [14] J. Kang, J. Yoon, K. Min, D. Yu, J. Nam, Y. Yang, and B. Kim, "A highly linear and efficient differential CMOS power amplifier with harmonic control," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 6, pp. 1314–1322, Jun. 2006.

- [15] P. Reynaert and S. Steyaert, "A 1.75-GHz polar modulated CMOS RF power amplifier for GSM-EDGE," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 12, pp. 2598–2608, Dec. 2005.

- [16] J. S. Walling, S. S. Taylor, and D. J. Allstot, "A class-G supply modulator and class-E PA in 130 nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 9, pp. 2339–2347, Sep. 2009.

- [17] V. Pinon, F. Hasbani, A. Giry, D. Pache, and C. Garnier, "A single-chip WCDMA envelope reconstruction

- LDMOS PA with 130 MHz switched-mode power supply," in *IEEE International Solid-State Circuits Conference Digest of Technical Papers*, San Francisco, CA, 2008, pp. 564–565.

- [18] G. Hanington, P. F. Chen, P. M. Asbeck, and L. E. Larson, "High-efficiency power amplifier using dynamic power-supply voltage for CDMA applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 47, no. 8, pp. 1471–1476, Aug. 1999.

- [19] W. Y. Chu, B. Bakkaloglu, and S. Kiaei, "A 10 MHz-bandwidth 2 mV-ripple PA-supply regulator for CDMA transmitters," in *IEEE International Solid-State Circuits Conference Digest of Technical Papers*, San Francisco, CA, 2008, pp. 448–449.

- [20] J. Choi, D. Kim, D. Kang, and B. Kim, "A new power management IC architecture for envelope tracking power amplifier," *IEEE Transactions on Microwave Theory and Techniques*, vol. 59, no. 7, pp. 1796–1802, Jul.

2011.

- [21] D. Kim, D. Kang, J. Choi, J. Kim, Y. Cho, and B. Kim, "Optimization for envelope shaped operation of envelope tracking power amplifier," *IEEE Transactions on Microwave Theory and Techniques*, vol. 59, no. 7, pp. 1787–1795, Jul. 2011.

- [22] S. Sakiyama, J. Kajiwara, M. Kinoshita, K. Satomi, K. Ohtani, and A. Matsuzawa, "An on-chip high-efficiency and low-noise DC/DC converter using divided switches with current control technique," in *IEEE International Solid-State Circuits Conference Digest of Technical Papers*, San Francisco, CA, 1999, pp. 156–157.

- [23] D. Kim, J. Choi, D. Kang, and B. Kim, "High efficiency and wide band envelope tracking power amplifier with sweet spot tracking," in *IEEE Radio Frequency Integrated Circuits Symposium*, Anaheim, CA, 2010, pp. 255–258.

Byungjoon Park received the B.S. degree in electrical engineering from Hanyang University, Seoul, Korea, in 2010 and is currently working toward the Ph.D. degree in electrical engineering from the Pohang University of Science and Technology (POSTECH), Pohang, Korea. His main interests are CMOS RF circuits for wireless communications, especially highly efficient

and linear RF transmitters and RF PA design.

Yunsung Cho received the B.S. degree in electrical engineering from Hanyang University, Ansan, Korea, in 2010 and is currently working toward the Ph.D. degree in electrical engineering from the Pohang University of Science and Technology (POSTECH), Pohang, Korea. His main interests are RF circuits for wireless communications, especially highly efficient and line-

ar RF transmitters and RF PA design.

Jooseung Kim Received the B.S. degrees in electrical engineering from the Pohang University of Science and Technology (POSTECH), Pohang, Korea, in 2010 and is currently working toward the Ph.D. degree in electrical engineering at POSTECH. His research interests are CMOS RF circuits for wireless communications with a special focus on highly efficient and linear

RF transmitter design.

Sangsu Jin received the M.S. degree in electrical engineering in 2005 from the Pohang University of Science and Technology (POSTECH), Pohang, Korea, where he is currently working toward the Ph.D. degree. From 2005 to 2011, he was with LG Electronics, Seoul, Korea, where he designed the low-noise amplifier for digital TV tuner integrated circuit (IC) and high-

speed serial/parallel links and all-digital PLL circuits for display interfaces. His research interests include RF PAs and CMOS RF/analog IC.

Daehyun Kang received the B.S. degree in electronic and electrical engineering from Kyungpook National University, Daegu, Korea, in 2006, and the Ph.D. degree in electrical engineering from Pohang University of Science and Technology (POSTECH), Pohang, Korea in 2012, respectively. He is currently with the Broadcom Corporation, Matawan, NJ, USA. His research

interests include the design of PAs and highly efficient and linear transmitter.

Bumman Kim (M'78 - SM'97 - F'07) received the Ph.D. degree in electrical engineering from Carnegie Mellon University, Pittsburgh, PA, in 1979. From 1978 to 1981, he was engaged in fiber-optic network component research with GTE Laboratories Inc. In 1981, he joined the Central Research Laboratories, Texas Instruments Incorporated, where he was involved in

development of GaAs power field-effect transistors (FETs) and monolithic microwave integrated circuits (MMICs). He has developed a large-signal model of a power field-effect transistor (FET), dual-gate FETs for gain control, high-power distributed amplifiers, and various millimeter-wave monolithic microwave integrated circuits (MMICs). In 1989, he joined the Pohang University of Science and Technology (POSTECH), Pohang, Korea, where he is currently a POSTECH Fellow and a Namko Professor with the Department of Electrical Engineering and Division of Information Technology Convergence Engineering (ITCE), and Director of the Microwave Application Research Center. He is involved in device and circuit technology for RF integrated circuits (RFICs) and PAs. He has authored over 300 technical papers. Prof. Kim is a member of the Korean Academy of Science and Technology and the National Academy of Engineering of Korea. He was an associate editor for the IEEE Transactions on Microwave Theory and Techniques, a Distinguished Lecturer of the IEEE Microwave Theory and Techniques Society (IEEE MTT-S), and an IEEE MTT-S Administrative Committee (AdCom) member.